▄▄▄▄· ▪ ▄▄▄▄▄▄▄▌ ▄▄ • ▐█ ▀█▪██ •██ ██• ▪ ▐█ ▀ ▪ ▐█▀▀█▄▐█· ▐█.▪██▪ ▄█▀▄ ▄█ ▀█▄ ██▄▪▐█▐█▌ ▐█▌·▐█▌▐▌▐█▌.▐▌▐█▄▪▐█ ·▀▀▀▀ ▀▀▀ ▀▀▀ .▀▀▀ ▀█▄▀▪·▀▀▀▀

ASIC roundup of open source RISC-V CPU cores

2022/01/18 Oguz Meteer // guztech

While waiting for simulation results for my final paper, I thought I’d synthesize and do place & route of several open source RISC-V CPU cores for fun. Some basic information:

- All CPU cores were synthesized using a well known 65 nm PDK.

- Synopsys Design Compiler with ultra effort was used for synthesis.

- Cadence Innovus was used for place & route.

- A standard I/O template was generated with Innovus with a square floorplan. This means that the area is most likely not used efficiently which will affect the utilization and maximum clock frequency.

- Only the CPU core with the register file and a standardized bus (Wishbone, AXI, AHB, etc.) was taken into account. No full SoCs were used to make the comparisons more fair.

- The goal was maximum clock frequency.

These results are just for fun and to give a very rough estimation of what could be achieved when implemented as an ASIC. There is no SoC, no interconnect, no SRAM, no off-chip memories, etc. so take these results with a mountain of salt. Still, I think it is interesting to see how cores meant to run primarily on FPGAs map onto an ASIC.

Also, since I went for the maximum clock speed, it increases the area quite a bit. To squeeze the last bit of performance out of a design, the usage of buffers shoots up, which increases area and power usage. So this choice negatively impacts cores that are optimized for area in a more disproportionate manner.

TL;DR

| Core | Instruction set | Max. Freq. (MHz) | Die area (mm^2) |

|---|---|---|---|

| SERV | RV32I | 1020 | 0.029584 |

| PicoRV32 | RV32I | 806 | 0.0425152 |

| Minerva | RV32IM | 625 | 0.051076 |

| Hazard3 | RV32I | 435 | 0.037401 |

| Hazard3 | RV32IMZbaZbbZbs | 400 | 0.05211128 |

| FemtoRV32 (quark)) | RV32I | 741 | 0.02964884 |

| FemtoRV32 (petitbateau) | RV32IMFC | WIP | WIP |

| VexRiscv (min) | RV32I | 606 | 0.04276588 |

| VexRiscv (IMAG) | RV32IMAC | 526 | 1.17332208 |

| Misato | RV32I | 667 | 0.04652624 |

| Misato (sky130) | RV32I | 75 | 0.25 |

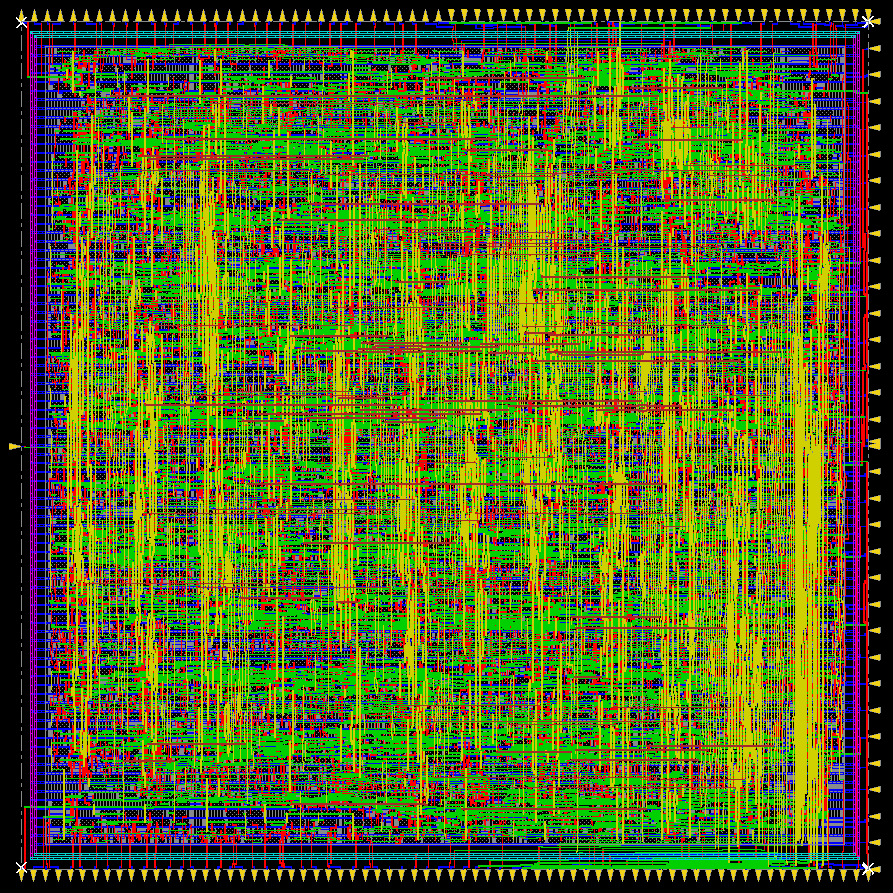

SERV (RV32I, RV32IM, RV32Zicsr)

The award-winning SERV CPU by Olof Kindgren is a bit-serial RISC-V CPU that is focussed on being as minimal as possible. It may not be the fastest CPU, but it is the (barely) smallest RISC-V CPU in this roundup (the other is the FemtoRV32-quark found further down in this post). Here, I used SERV version 1.1.0 with the default configuration (RV32I).

- Maximum clock frequency: 1020 MHz

- Die area: 0.029584 mm^2

- Utilization rate: 78.868%

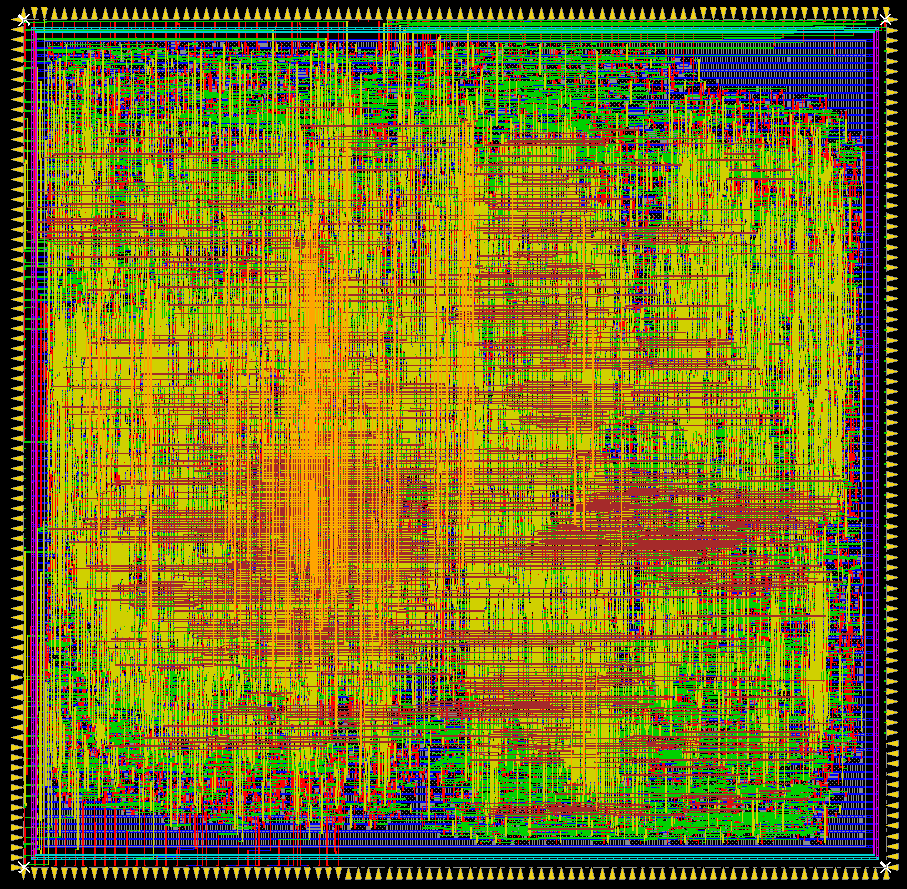

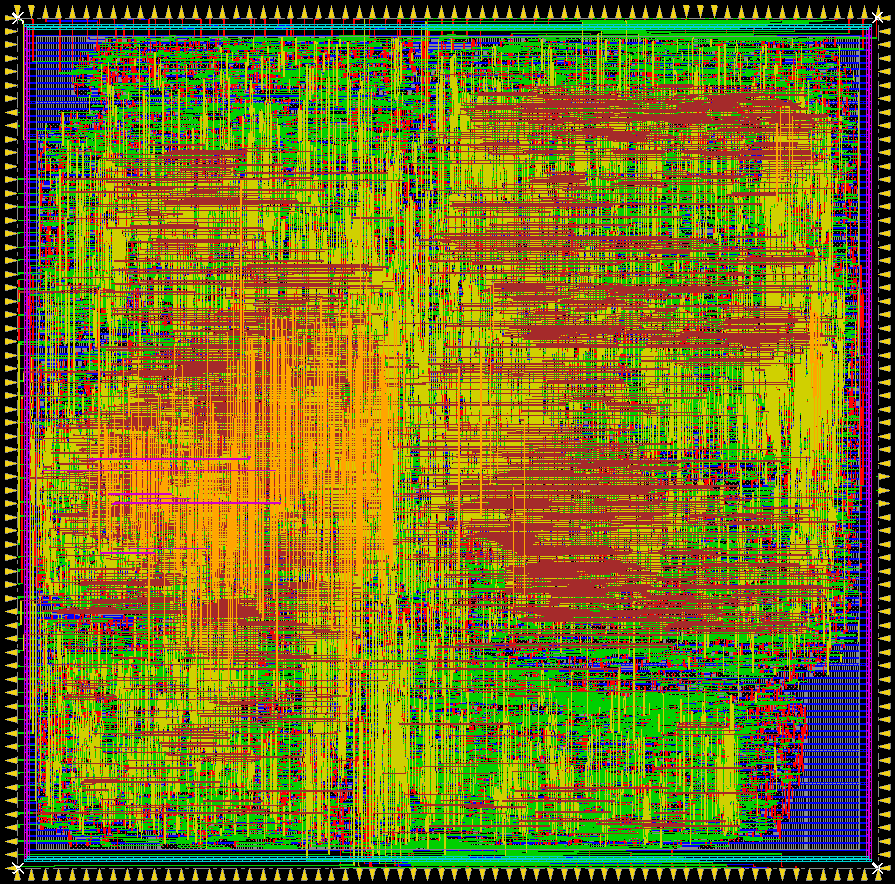

PicoRV32 (RV32E, RV32I, RV32IC, RV32IM, RV32IMC)

The excellent size-optimized PicoRV32 CPU by Claire Xenia Wolf is not only a very flexible core, but it’s also the first formally verified RISC-V CPU! The default configuration was used (RV32I).

- Maximum clock frequency: 806 MHz

- Die area: 0.0425152 mm^2

- Utilization rate: 77.703%

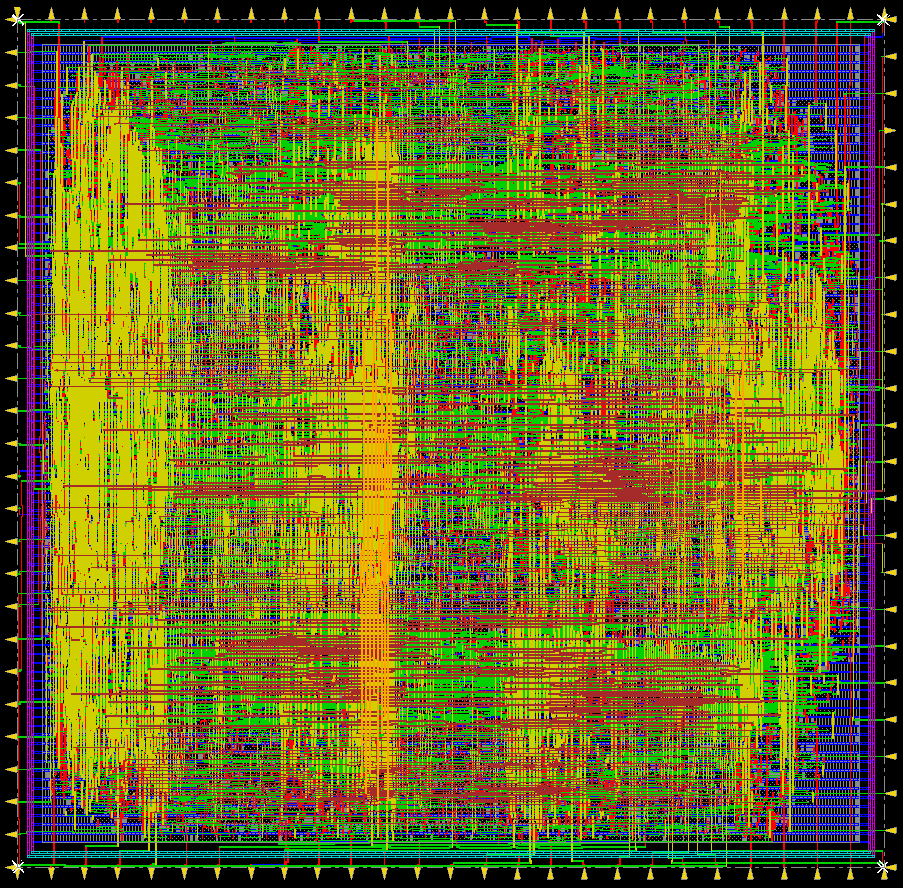

Minerva (RV32IM)

The Minerva CPU by Lambda Concept is a configurable, 6 stage RISC-V CPU written in Amaranth HDL which is a hardware description language written in Python. The default configuration was used (RV32IM, no I$ / D$).

- Maximum clock frequency: 625 MHz

- Die area: 0.051076 mm^2

- Utilization rate: 80.435%

Hazard3 (RV32I + M, C, A, Zicsr, Zba, Zbb, Zbc, Zbs)

The Hazard3 CPU core by Luke Wren is a 3-stage RISC-V processor that also supports a bunch of optional extensions. Two different versions were used (both use hazard3_cpu_1port).

RV32I

- Maximum clock frequency: 435 MHz

- Die area: 0.037401 mm^2

- Utilization rate: 75.855%

- CoreMark/MHz: 1.13

RV32IMZbaZbbZbs

- Maximum clock frequency: 400 MHz

- Die area: 0.05211128 mm^2

- Utilization rate: 77.937%

- CoreMark/MHz: 3.02

(WIP) FemtoRV32 (RV32I, RV32IM, RV32IM, RV32IMC, RV32IMFC)

The FemtoRV32 CPU core by Bruno Levy is part of his learn-fpga teaching material for FPGAs and processor design. Two different versions were used: quark (RV32I) and petitbateau (RV32IMFC). Important to note is that both versions don’t use a standardized interface.

Quark (RV32I)

- Maximum clock frequency: 741 MHz

- Die area: 0.02964884 mm^2

- Utilization rate: 80.173%

Petitbateau (RV32IMFC)

- Maximum clock frequency: ** MHz**

- Die area: ** mm^2**

- Utilization rate: %

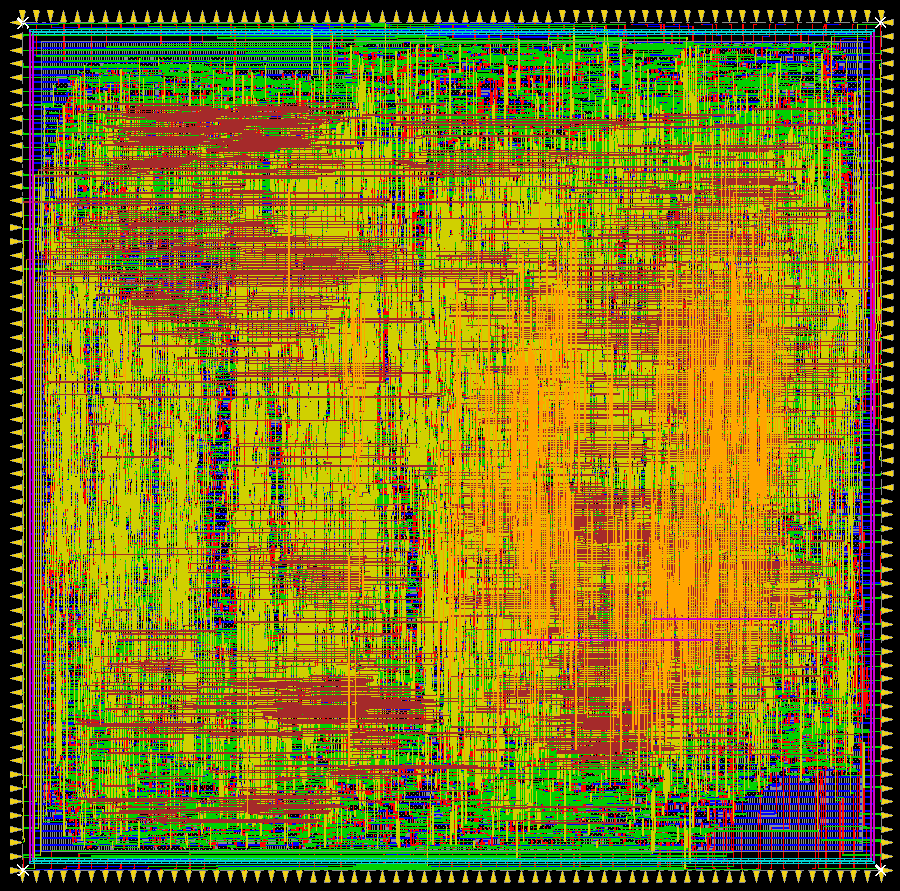

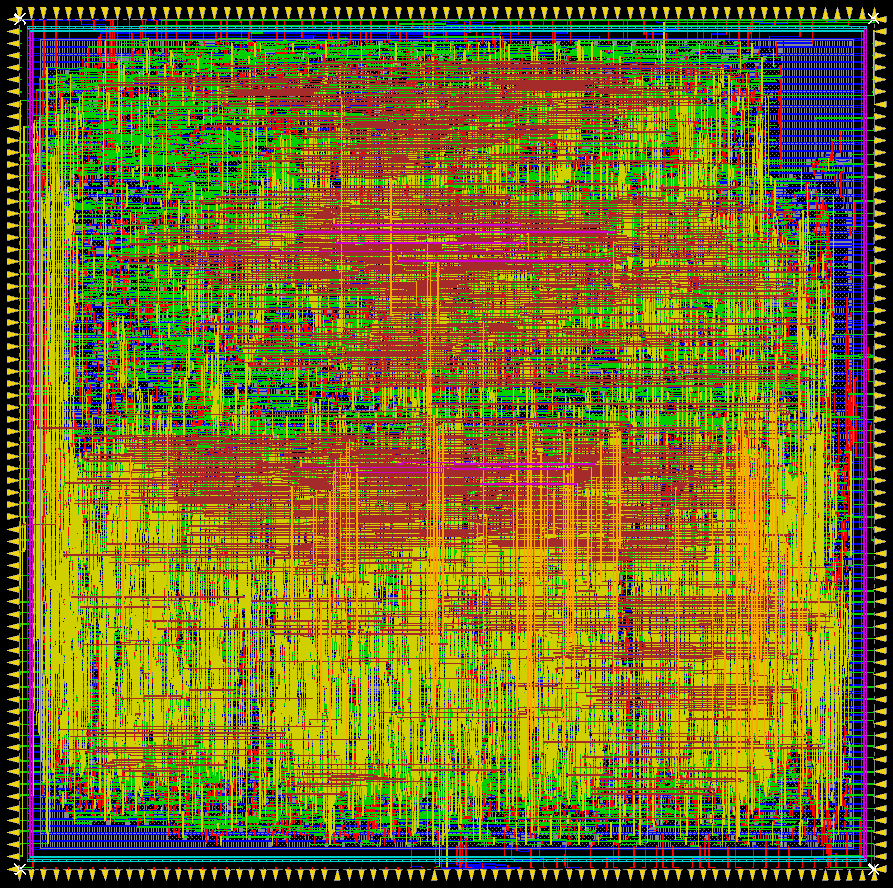

VexRiscv

The VexRiscv CPU core by Charles Papon is an award-winning core that is written in SpinalHDL which is also being developed by him. It is one of the most flexible and best performing RISC-V implementations, capable of being able to run Linux. It is used by default in LiteX. Two different configurations were used: min (RV32I) and IMAC (RV32IMAC).

VexRiscv (min)

- Maximum clock frequency: 606 MHz

- Die area: 0.04276588 mm^2

- Utilization rate: 79.093%

VexRiscv (IMAC)

- Maximum clock frequency: 526 MHz

- Die area: 1.17332208 mm^2

- Utilization rate: 82.824%

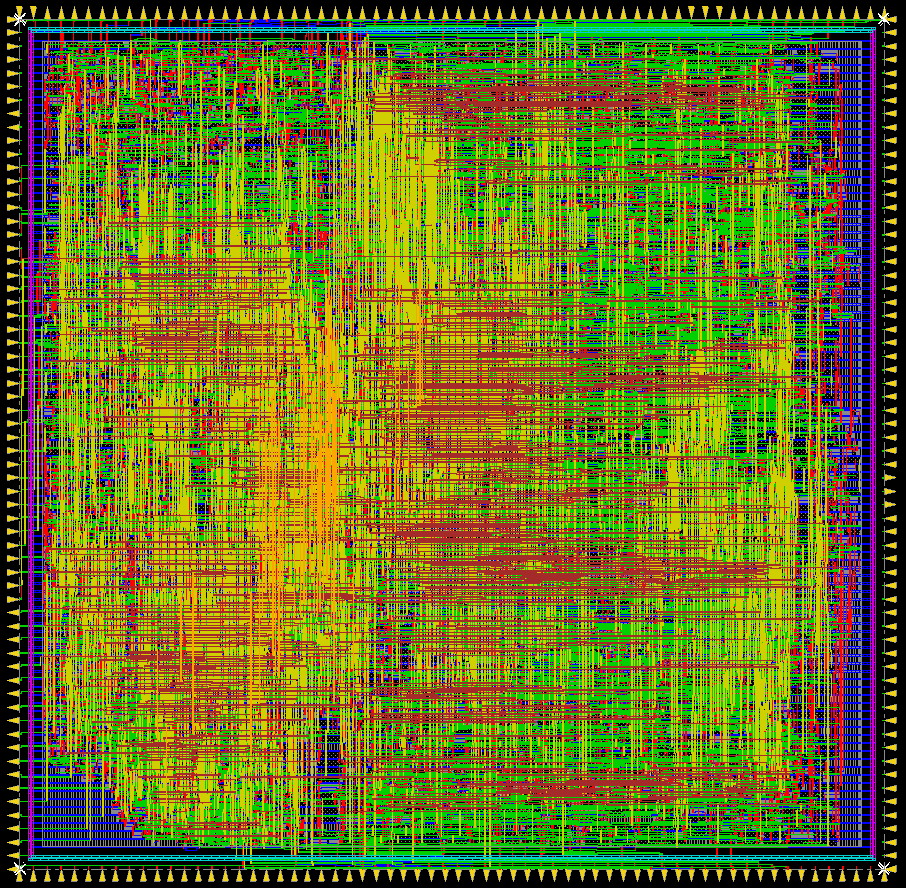

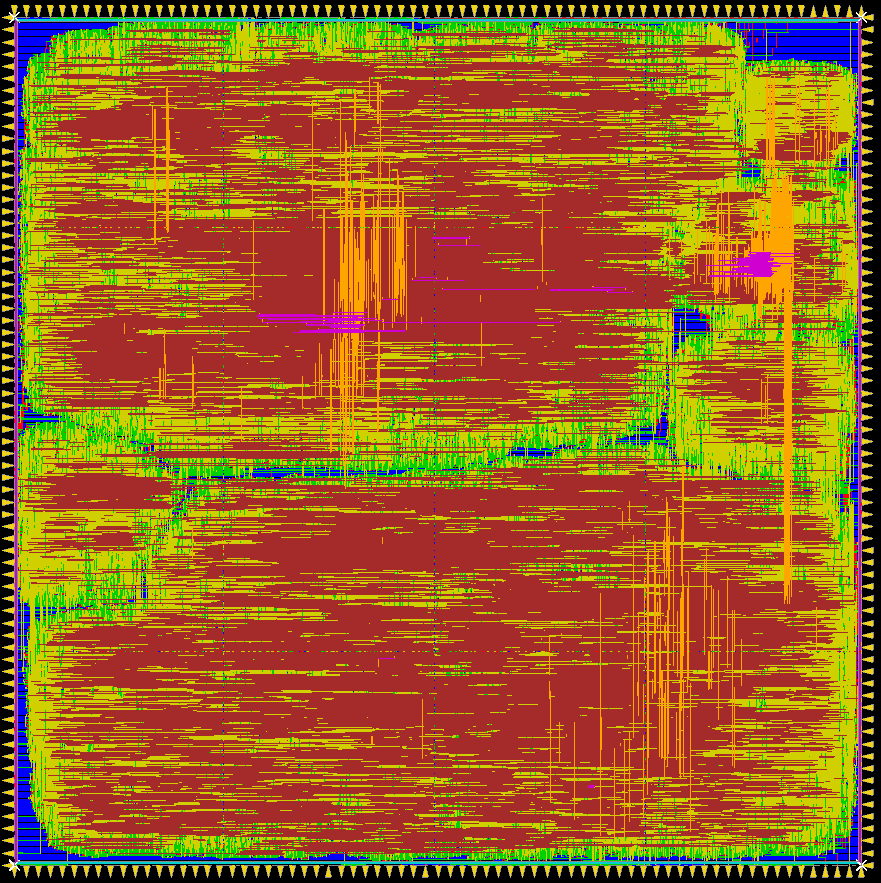

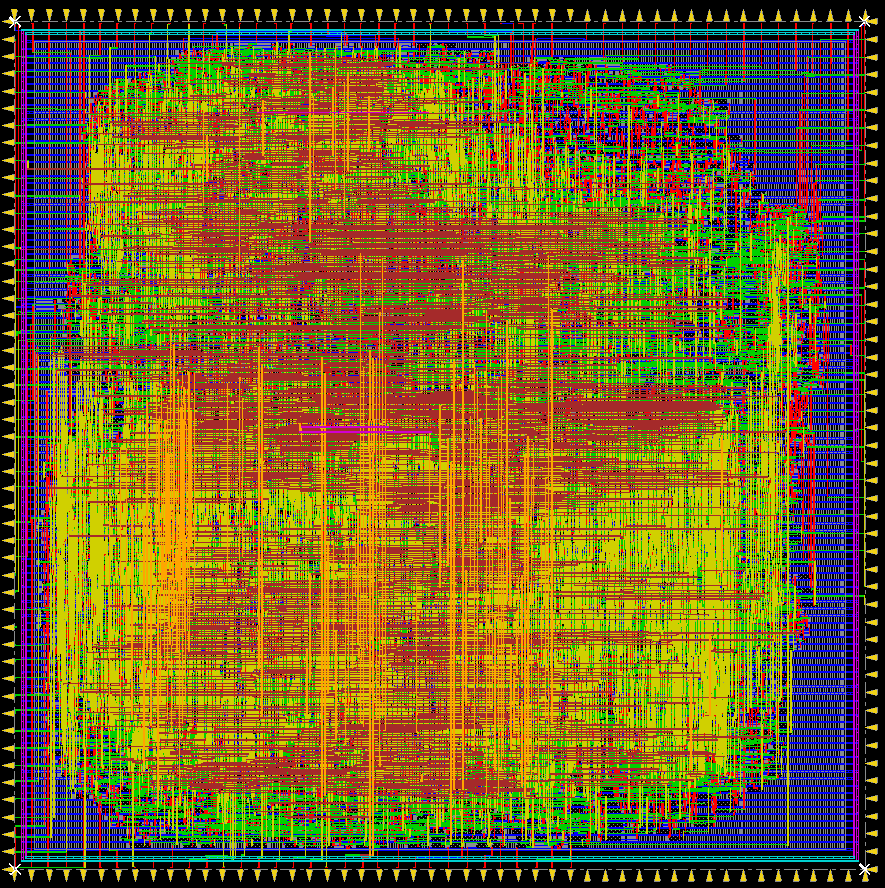

Misato (RV32I)

The Misato core developed by me is written in Amaranth HDL and currently does not use a standardized interface (I am working on adding a Wishbone interface). It is very bare bones, but parts of it are formally verified. Currently, the core does require a single cycle instruction and data memory for it to work correctly. It is a work in progress, but I wanted to include it anyway.

- Maximum clock frequency: 667 MHz

- Die area: 0.04652624 mm^2

- Utilization rate: 64.553%

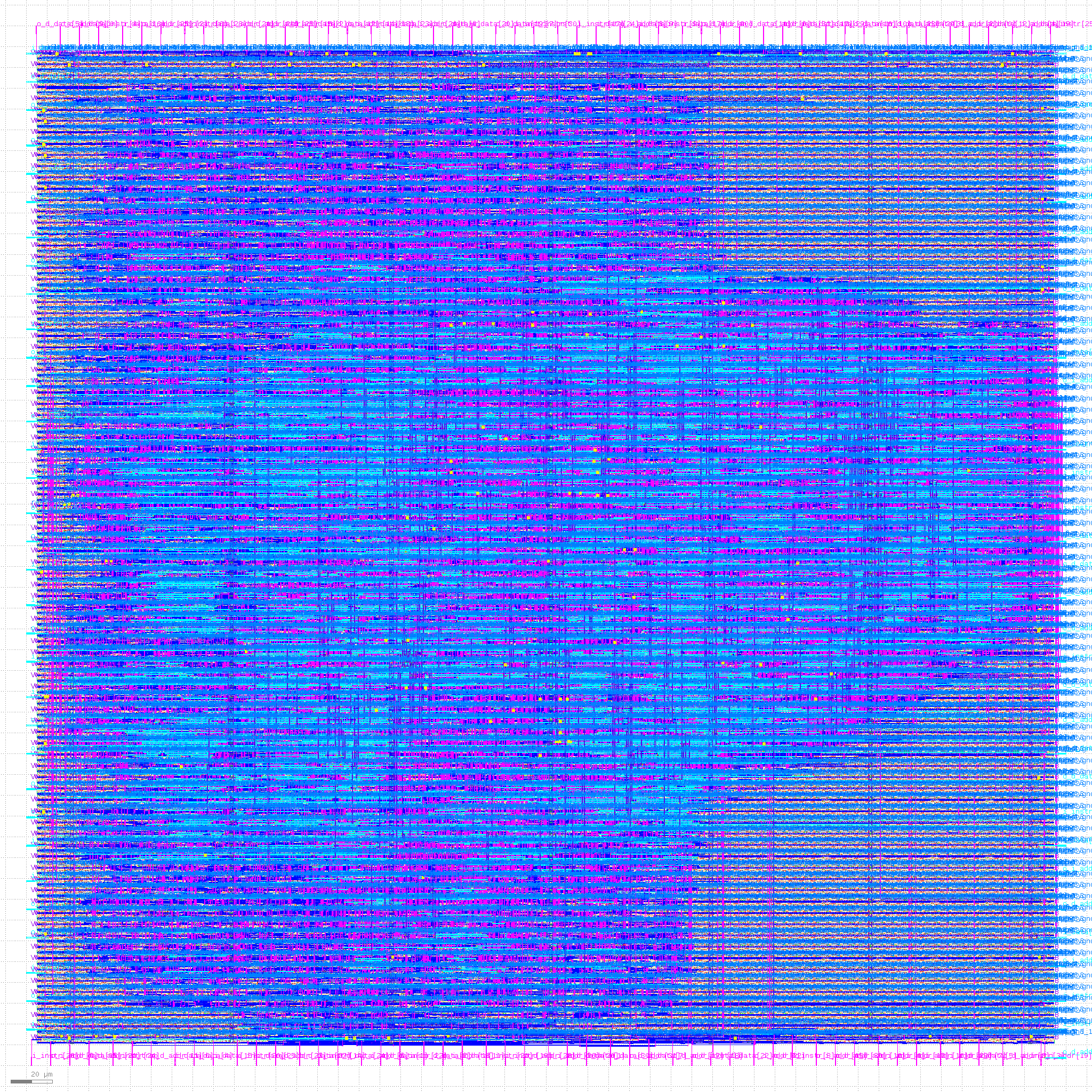

SkyWater 130 nm version

Olof Kindgren added FuseSoC support for Misato, which means it can now also be built with the SkyWater 130 nm PDK!

- Maximum clock frequency: 75 MHz

- Die area: 0.25

- Utilization rate: 70%

If you have questions and/or constructive criticism, let me know on Twitter @BitlogIT